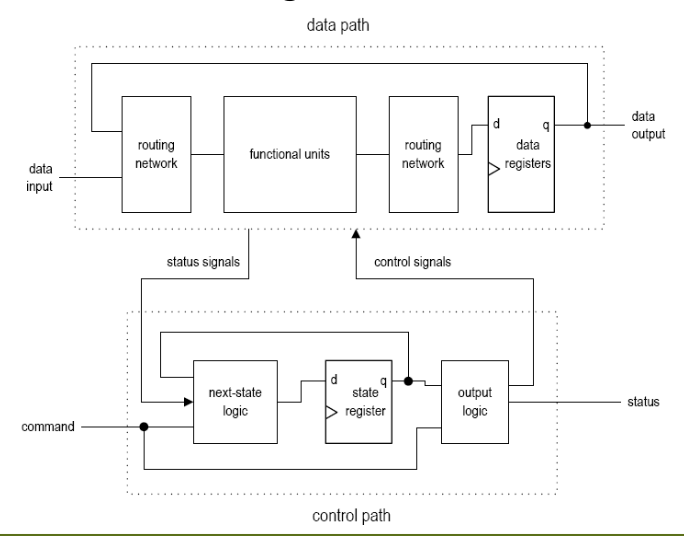

Continuación del block diagram de 20201015 - VHDL 5 - Diseño secuencial.

FSMD es la implementación de “dataflow” en VHDL.

Convertir algoritmo en circuito combinacional sin elementos de memoria. La secuencia será “flow of data”.

Problemas:

- Poco flexible

- Valida unicamente para algoritmos triviales

Bloque FSMD

Construcción del datapath:

- lista todas las operaciones RT (register transfer)

- Agrupar operaciones RT de acuerdo con el registro destino

- Añadir lógica combinacional

- Añadir status circuits

Construcción del control path:

- Listar todas las entradas de control

- Entradas de control externas

- Señales que determinan un estado siguiente

- Nuevos circuitos para generar lógica

- Listar todas las salidas de control

- Señales de control para multiplexores

- Señales de control externas

- Seguir la construcción estándar FSM

Periodo de reloj y rendimiento

Dificil de analizar porque hay dos bucles

Mejor escenario -> Las señales de control se necestan tarde, las señales de estados se disponen pronto

$$ T_c = T_{cq}(data) + T_{dp} + T_{setup}(data) \\ T_c = T_{cq}(state) + T_{output} + T_{dp} + T_{next} + T_{setup}(state) \\ T_{cq} + T_{dp} + T_{setup} \le T_c \le T_{cq} + T_{output} + T_{dq} + T_{next} + T_{setup} \\ \frac{1}{T_{cq} + T_{output} + T_{dq} + T_{next} + T_{setup}} \le f \le \frac{1}{T_{cq} + T_{dp} + T_{setup}} \\ T_c = \text{Clock period} \\ K = \text{nº de ciclos para completar la computación} \\ Total = latencia = K \cdot T_c \\ $$

En donde K viene determinada por el algoritmo.