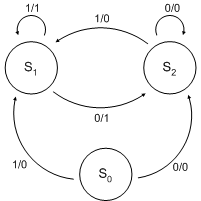

Se utilizará el ejemplo de una máquina Mealy:

Donde:

- S es el estado, como IDLE, END, etc.

- x/y donde

xes la entrada que hace que se cumpla esa transición eyes la salida. Un ejemplo podría serx==1/led=1

En VHDL una máquina de estados se hace de la siguiente forma:

type t_SM_Main is (s_Idle, s_TX_Start_Bit, s_TX_Data_Bits,

s_TX_Stop_Bit, s_Cleanup);

signal r_sm_main : t_SM_Main := s_Idle;

...

case r_sm_main is

when s_Idle =>

-- CODE

r_sm_main <= s_TX_Start_Bit; -- Example

when s_TX_Start_Bit =>

-- CODE

when s_TX_Data_Bits =>

-- CODE

when s_TX_Stop_Bit =>

-- CODE

when s_Cleanup =>

-- CODE

when others =>

r_sm_main <= s_Idle;

end case;