Serie o paralelo (Hace años)

Serie:

- Menos pistas

- Menos velocidad

- Más distancia

Paralelo:

- Más pistas

- Más velocidad

- Menos distancia

Buses Serie

Se emplean para la interconexión de chips/periféricos/memorias/sensores… En la misma placa o entre placas.

Buses seria asíncronos:

- UART/USART

- RS-232C

Síncronos:

- SPI

- I2C

- Específicos

- OneWire

SPI: Serial Peripheral Interface

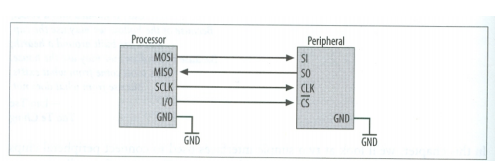

Bus Síncrono Maestro/Esclavo de 4 hilos. Los dispositivos se actian con el CS. Se utiliza para conexión de periféricos con necesidad de alta tasa binaria (<100Mbps)

En maestro:

- MISO

- MOSI

- SCLK

- I/O

En esclavo:

- SDI (Slave Data In)

- SDO (Slave Data Out)

- CLK

- CS

Modos de operación:

- Polaridad “Low” (Reloj normalmente en bajo) en fase 0. Se envia cuando clk flanco de subida

- Polaridad “Low” en fase 1. Se envia cuando clk flanco de bajada

- Los modos polaridad “High”, es lo mismo que lo anterior pero el clk está normalmente en alto.

I2C: Inter Integrated Circuit

Bus con protocolo síncrono Maestro/Esclavo a 2 hilos Terminación (Open Collector/drain). Recuerda que se necesita de resistencias pull up para que funcione, el valor típico es 10k, pero en este link te pone cómo se calcula

Dos hilos:

- SDA (Serial Data)

- SCL (Serial Clock)

Características:

- Bidireccional (detecta colisión)

- Sincrono

- Multimaster. El maestro gestiona el reloj

Se utiliza para conexión de periféricos con baja tasa binaria. Original 100 kbps, fastmode 400 kbps, highspeed 3.4MHz. Los anteriores bidireccional. UltraFast unidireccional a 5 MHz.

Este tipo de bus implica que todos los dispositivos conectados en el bus tienen que estar encendidos todo el tiempo. Puede ser problematico en topologías para dispositivos de baja potencia.

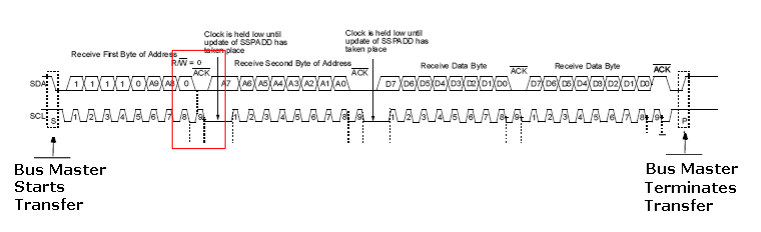

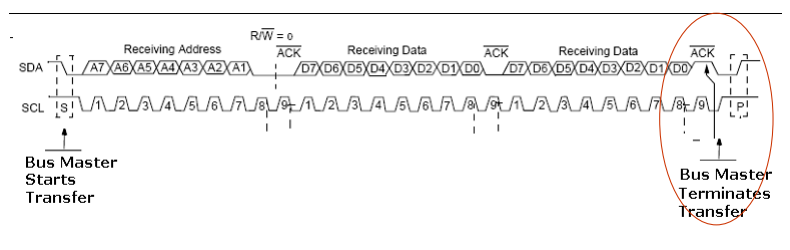

Transferencias I2C

Condición de inicio: El master cambia la línea de datos (SDA) con el reloj (SCL) constante.

Luego envía la trama. Cada campo de la trama es un byte + 1 bit de ACK. Se envían campos secuencialmente. Byte a byte, MSB primero.

Cada bit se valida con el SCL. El dato (SDA) no puede variar hasta que el reloj (SCL) vuelve a cero.

Condición de final: El que hace de master cambia la línea de datos (SDA) con el reloj (SCL) constante.

El primer/segundo byte es la dirección del chip direccionado. Si es dirección standard tiene 7 bits, si es extendida 11 bits. El último bit de la dirección indica el sentido de la transferencia (lectura 1/escritura 0).

Algunas direcciones reservadas:

- 1er byte 0x00 => General call

- 2º byte Tipo de general call:

- 0x06 => Reset y envía tu dirección

- 0x04 => Envía tu dirección sin reset

Si la dirección es extendida (10 bits) es como en la figura. El bit de lectura/escritura es el último del primer byte.