Ejercicio ASMD

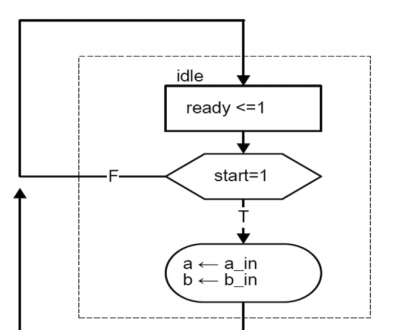

Siempre poner al principio del diagrama alguna estructura como esta:

Donde normalmente tenemos 3 estados, idle, op y done.

Es mejor poner en el último estado una señal done_tick que se activará en el controlPath cuando estado_reg tenga el estado done.

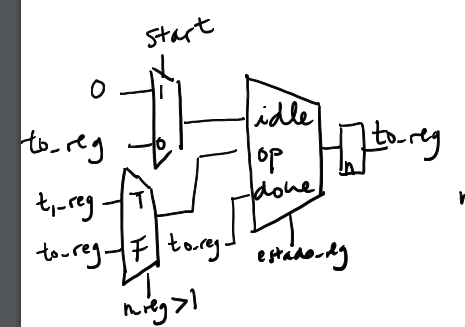

Estructura típica de un registro que se actualiza. Parte del datapath:

Cuando hay que hacer el pseudo código es común hacer lo siguiente:

- Las entradas se instanciarán de la siguiente forma:

n <- n_in - Las variables se pondrán secuenciales de la siguiente forma

t1, t2, t3

Arquitecturas

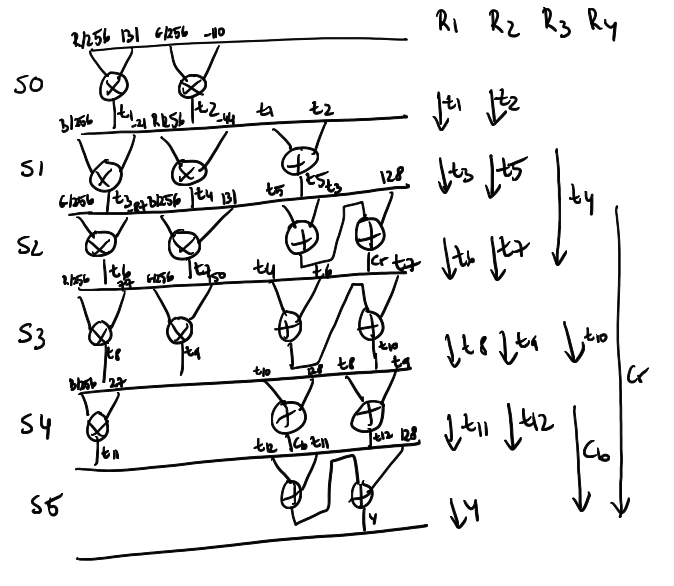

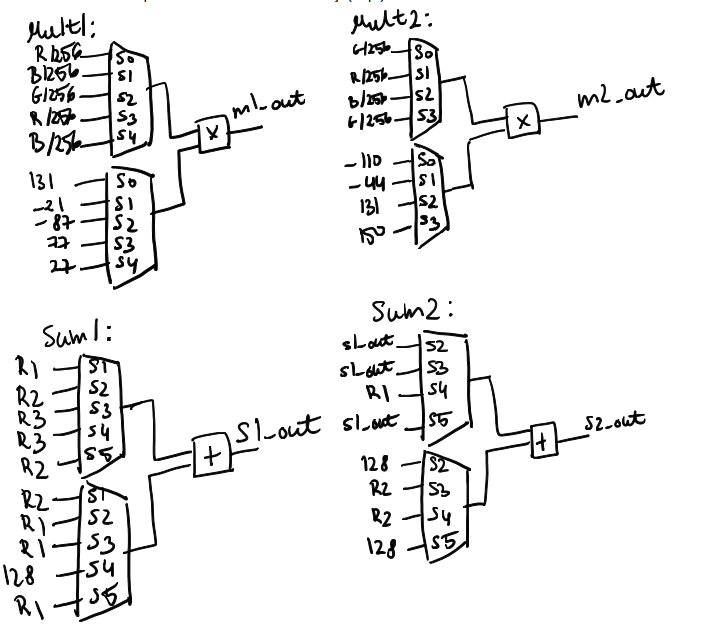

Ejemplo de cómo se hacen las arquitecturas:

Cuidado con estos ejercicios. Si pone que tarda 1 ciclo de reloj significa que puede poner la salida en la entrada de otra en la siguiente etapa (incluso en la misma)… pero si pone que tarda 2 ciclos no se puede hacer. Normalmente los sumadores puede poner su salida a la entrada de otro en la misma etapa, pero no los multiplicadores.

Cuidado con estos ejercicios. Si pone que tarda 1 ciclo de reloj significa que puede poner la salida en la entrada de otra en la siguiente etapa (incluso en la misma)… pero si pone que tarda 2 ciclos no se puede hacer. Normalmente los sumadores puede poner su salida a la entrada de otro en la misma etapa, pero no los multiplicadores.

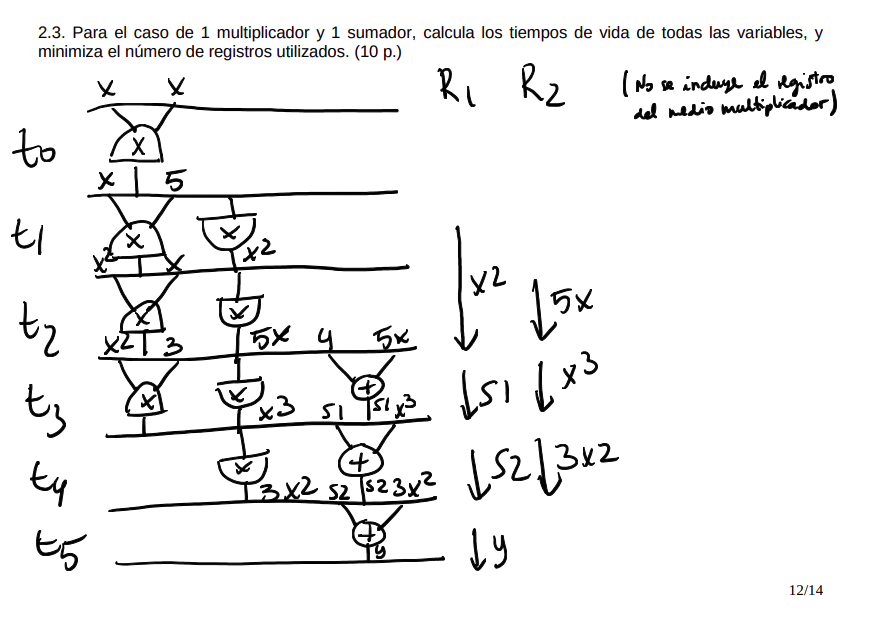

A la hora de poner las variables a los registros es mejor agruparlas, es decir, todas las multiplicaciones en un registro y todas las sumas en otro. Luego eso hará que sea más fácil hacer el dibujo.

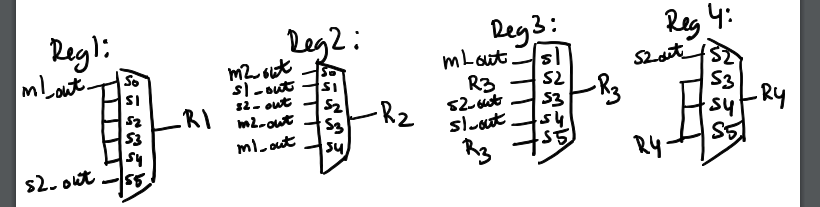

En este ejercicio pasa una cosa curiosa. El multiplicador utiliza dos ciclos de reloj. Lo importante es darse cuenta cómo se utiliza R1 y R2, que se instancia cuando el resultado de la operación está disponible, que esto es 1 ciclo después de la operación:

La ruta Datapath se hará de la siguiente forma:

Temporización

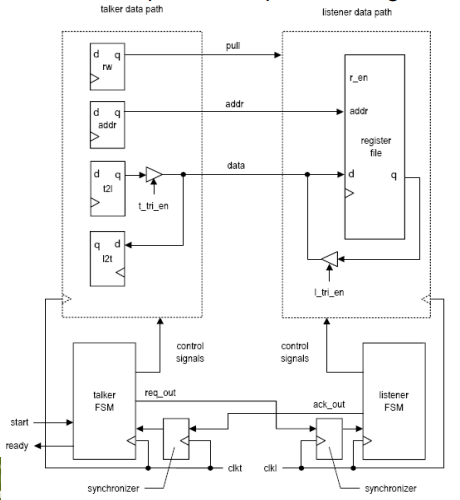

Propuesta de un sincronizador de bus de datos