Elementos de una jerarquía de memoria

Niveles de jerarquía de memoria

- El procesador solicita un item al nivel más alto (caché L1)

- Si el item esta en el nivel

- Se produce un acierto (hit)

- Se accede al item

- Si el item no está en el nivel

- Se produce un fallo

- Se solicita al nivel inferior

- El bloque se copia y se accede al item

- Métricas

- Tasa de aciertos (hit ratio) = aciertos/accesos

- Tasa de fallos (miss ratio) = fallos/accessos = 1 - hit ratio

- Tiempo de acierto = Obtener acierto/fallo + tiempo de acceso

- Tiempo de fallo = Reemplazar bloque + tiempo de acierto

Diseño de la jerarquía de memoria

- Reducir la latencia (penalización por fallo)

- Aumentar ancho de banda

Memorias caché

Caché: memoria rápida organizada en \(2^n\) líneas:

- Cada linea almacena las palabras de un bloque.

- La caché se carga por bloques dsde el inferior

- Utilizan tecnología SRAM

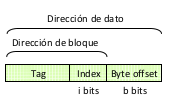

Caché de mapeo directo

- Indice (index): bits inferiores de la dirección del bloque

- Etiqueta (tag): bits superiores de la dirección del bloque

- Posición = (dirección del bloque) mod (bloques en la caché)

- Tamaño caché \(2^i\) bloques

- Tamaño bloque \(2^b\) bytes

La dirección de la linea nos la da index.

La dirección de la linea nos la da index.

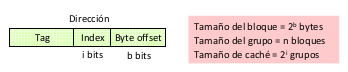

Cachés asociativas

Resolverán el problema de acceso alternativo a dos bloques con la misma dirección

Se organizan en grupos (sets) de n líneas con el mismo índice

A medida que crece la asociatividad reduzco fallos pero aumento coste.

A medida que crece la asociatividad reduzco fallos pero aumento coste.

Actualización de escrituras en memoria

- Escritura (store) en un blooque que está en caché

- Hay que actualizar el contenido en memoria

- Estrategias de actualización en memoria

- Write-through: La memoria se actualiza inmediatamente

- Write-back: La memoria se actualiza en un momento posterior

- Escritura en un bloque que no está en caché

- Write-allocate: Traer el bloque a la caché

- Write-around: A veces con write-through no se trae el bloque

Write-through: Escribir en memoria inmediatamente

Las escrituras (store) tardan más. Solución: Utilizar un buffer de escrituras (Write buffer) -> Almacena los datos pendientes de escritura en memoria. Cuando se reemplaza se puede usar el buffer de escritura.

Write-back: Escribir en memoria al reemplazar el bloque

Hay que marcar el bloque como no actualizado (dirty). Cuando se reemplaza puede utilizar el bloque de escrituras. Solo se escribe en memoria cuando hay fallos y hay que sustituir.

Prestaciones de un sistema con cachés

$$ C_{Mem-stall} = \text{Accesos} \cdot \text{Tasa de fallos} \cdot \frac{\text{Penalización}}{\text{fallo}} \\ C_{Mem-stall} = \text{IC} \cdot \frac{\text{Fallos}}{\text{instrucción}} \cdot \frac{\text{Penalización}}{\text{fallo}} $$

Los accesos:

- datos (load/store) (% suyo)

- instrucciones (100%)

Tiempo medio de acceso a memoria: AMAT

$$ \text{AMAT} = \text{Tiempo de acierto} + \text{Tasa de fallos} \cdot \frac{\text{Penalización}}{\text{fallo}} $$

Cachés multiniel

- Caché(s) de primer nivel (L1) pequeños pero rápidos y se conecta a la CPU

- Caché(s) de niveles inferiores (L2 y L3)

- L3 en sistemas de gama alta. La L2 atiende los fallos de L1 (L3 los de L2). Son más grandes y menos rápidos que las L1. Se optimizan para reducir la tasa de fallos

Tipos de fallos en cachés

- Fallos inevitables -> La primera vez que se acceder a un bloque

- Fallos por capacidad -> Debidos al tamaño limitado de la caché. Cuando se vuelve a acceder a un bloque que ha sido sustituido. Se definen en cachés completamente asociativos.

- Fallos por conflicto o colisión -> en cachés que no sean completamente asociativos. Debidos a la competencia por posición dentro de un grupo.

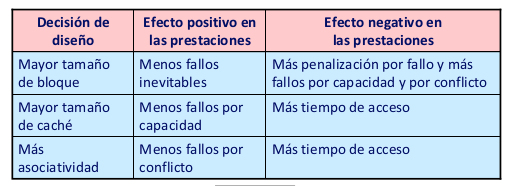

Compromisos en el diseño de cachés

Gestión del sistema de memoria

Memoria virtual

Extender el concepto de caché a la memoria principal respecto al almacenamiento secundario.

-

Traducción de direcciones virtuales a fisicas

- La CPU solicita direcciones virtuales a la memoria física

- Hay que traducir direcciones virtuales a direcciones físicas

-

Página: Bloque de memoria con direcciones consecutivas

- Fallo de página: se solicita un dirección que no está en la memoria principal.

- Hay que traer la página del disco dura.

- Tarda millones de ciclos de reloj.

- Se encarga el sistema operativo (page fault handler)

Tablas de páginas

Almacena información sobre la ubicación de las páginas. Consiste en un array de entradas PTE (Page table entry). Se indexan con el número de página virtual.

- Detección de fallos de página

- Valid = ‘1’ -> está en memoria

- Dirty = ‘1’ -> ha sido escrita -> store

- Ref = ‘1’ -> ha sido referenciada

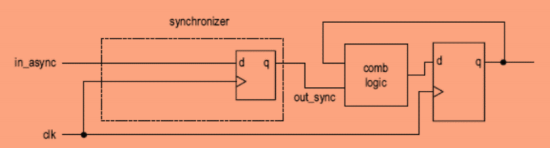

Bufer de traducción paralela (TLB)

Cada acceso a memoria desde programa requiere dos accessos a memoria principal. Es una caché rápida de PTE’s en la CPU.